IIC相关内容的记忆

2017-02-15

本文的内容 仅仅是为了能够回想起IIC相关内容, 并不求严谨和准确.

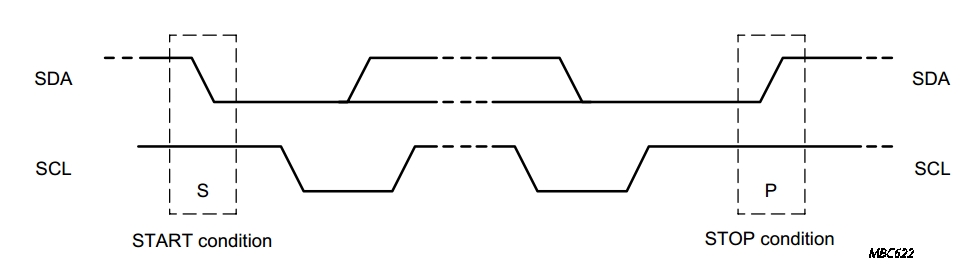

1. 起始和停止信号

因为上拉省电, 所以, 空闲时, SDA是上拉的. 在时钟为高时, SDA若表示数据, 需维持稳定, 否则, 其表示起始或停止.

2. 数据的组织 和 表示

假定是7bit地址的情况.

先发送高位还是低位?

可以考虑/回忆下 7bit地址+1bit读写 时的情况, 我们是先发送地址的, 所以, 是先发送高位, 后发送低位的.

最常见的是r/w# 所以,读为1, 写为0.

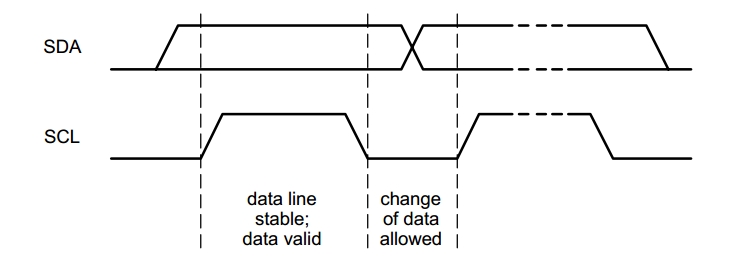

时钟有, 代表心脏还在跳, 器件还在工作, 所以, 在SCL高电平时对SDA采样作为数据.

如SCL高电平时, SDA发生了转换, 那么, 就不是在传送数据, 而是表示起始或停止.

3. 异常处理

ACK: 接收到8bit数据的要回复ACK, 这样是9bit. master端发送7bit地址+1bit读写, slave回复ACK, 也是9bit, 形式上统一.

ACK要能够被检测到, 故不发送ACK的那方不能去干扰SDA, 故保持高电位, 发送ACK的那方拉低SDA.

如果 从机接收好完整的数据字节(含响应位) 后, 要完成一些其他功能后 (例如一个内部中断服务程序), 才能接收或发送下一个完整的数据字节, 可以使时钟线 SCL 保持低电平迫使主机进入等待状态.

本文地址: https://awakening-fong.github.io/posts/hw/iic

转载请注明出处: https://awakening-fong.github.io

若无法评论, 请打开JavaScript, 并通过proxy.

blog comments powered by Disqus